# RESILIENT AND SECURE DEEP LEARNING-ORIENTED MICROARCHITECTURES

Brunno Figueirôa Goldstein

Tese de Doutorado apresentada ao Programa de Pós-graduação em Engenharia de Sistemas e Computação, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Doutor em Engenharia de Sistemas e Computação.

Orientadores: Felipe Maia Galvão França Sandip Kundu Alexandre Solon Nery

Rio de Janeiro Junho de 2022

## RESILIENT AND SECURE DEEP LEARNING-ORIENTED MICROARCHITECTURES

Brunno Figueirôa Goldstein

TESE SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM CIÊNCIAS EM ENGENHARIA DE SISTEMAS E COMPUTAÇÃO.

Orientadores: Felipe Maia Galvão França Sandip Kundu Alexandre Solon Nery

Aprovada por: Prof. Felipe Maia Galvão França Prof. Sandip Kundu Prof. Alexandre Solon Nery Prof. Claudio Luis de Amorim Prof. Mauricio Lima Pilla Prof. Ricardo Augusto da Luz Reis Prof. Diego Leonel Cadette Dutra

> RIO DE JANEIRO, RJ – BRASIL JUNHO DE 2022

Goldstein, Brunno Figueirôa

Resilient and Secure Deep Learning-Oriented Microarchitectures/Brunno Figueirôa Goldstein. – Rio de Janeiro: UFRJ/COPPE, 2022.

XVIII, 118 p.: il.; 29,7cm.

Orientadores: Felipe Maia Galvão França

Sandip Kundu

Alexandre Solon Nery

Tese (doutorado) – UFRJ/COPPE/Programa de Engenharia de Sistemas e Computação, 2022.

Referências Bibliográficas: p. 105 – 117.

Deep Neural Networks.

Hardware Dependability.

Resiliency.

Security.

França, Felipe Maia Galvão et al. II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia de Sistemas e Computação.

III. Título.

Dedicated to my beloved daughter Helena and wife Juliana, and my parents, Adecy and Ricardo.

# Acknowledgements

To the committee members for kindly taking their time to evaluate this work and propose important feedback.

To my advisors, Felipe França, Sandip Kundu, and Alexandre Nery, for their dedication, inspiration, and ideas during the whole development process of this thesis. Without you, this work would not be feasible. Thank you for your wisdom and friendship.

To all authors cited in this work. This work would not be possible without the knowledge provided by you.

To Leandro Marzulo for presenting the academic life and advising me during my master's and Ph.D. Thank you for being such a friend, life advisor, and inspiration for me and several other students. The world needs more people like you.

To everyone at the department PESC/COPPE/UFRJ who makes the engines run. Your work makes students' lives less stressful by removing the heavy burden of bureaucracy and leaving our time entirely dedicated to the thesis development. To cite a few: Ricardo, Gutierrez, Mercedes, Cláudia. Similarly, to all the professors who make this department so singular and extraordinary. In particular, prof. Valmir Barbosa, prof. Claudio Amorim, prof. Guilherme Travassos and prof. Nelson Maculan.

To Coordenação de Aperfeiçoamento de Pessoal de Nível Superior (CAPES Foundation) for providing a full-time scholarship in Brazil and a one-year scholarship as a visiting scholar at the University of Massachusetts, Amherst - US, making possible the development of this work.

To NGD Systems for investing in conjoint research within our laboratory.

To Intel Labs India for the knowledge, guidance, support through the development of this work, and the opportunity for the full-remote ten-month internship. In particular, Sudarshan Srinivasan, Kaul Bharat, and Pradeep Dubey.

To all my beloved friends that I made during this journey. The adventure would probably have become a nightmare without you. By putting some light into the darkness with smiles, jokes, guidance, or even small talk, you not only made this work possible but also forged the human that I have become. Hopefully, I will not miss anyone here. Friends from Mamatinha: Israel, Dani, Renan, Rebeca, Hugo, Spencer, Ana, Pedro, Moyses, Natália, Evandro, and Dani Castelo. Family from LAM: Santiago, Victor, Leopoldo, Hugo, Rui, Diego, and my former students Alan and Pedro. Friends from UMass: Vinay and Nazmul. Family from North Village: Felipe, Nur, Maria, Cecília, Brenno, and Pri. Friends from UERJ: Brazil, Ingrid, Ítalo, Denilson, Mentira, and Wellington. Friends at SC18: Julia, Ana, and Rafa.

To Victor, Santiago, and Leopoldo for their friendship, support, and collaboration during my whole Ph.D. LAM will never be the same without you.

Finally, to my family. To my beloved daughter Helena who was born and raised during the development of this work. Thank you for your love and kindness. To my wife Juliana, who supported me even before the Ph.D. Nothing of this would be possible without you. Thank you for your love, support, patience, and always believing in me – the best is yet to come. To my parents, Adecy and Ricardo, for the love, dedication, support, and patience. To my brothers, Rafael, and Ricardo, for the inspiration and support. To my dog Mel who always is there to give love and support.

Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Doutor em Ciências (D.Sc.)

## MICROARQUITETURAS ORIENTADAS A REDES NEURAIS PROFUNDAS RESILIENTES E SEGURAS

Brunno Figueirôa Goldstein

#### Junho/2022

Orientadores: Felipe Maia Galvão França Sandip Kundu Alexandre Solon Nery

Programa: Engenharia de Sistemas e Computação

Redes Neurais Profundas (RNP) emergiram como uma importante solução para problemas complexos de diversas áreas, tais como visão computacional, processamento de linguagem natural e sistemas de recomendação. Um sistema ideal baseado em RNP deveria, de forma precisa, realizar predições e classificações utilizando-se de entradas quaisquer mas sem interferência do ambiente externo. Contudo, os sistemas baseados em RNP são suscetíveis a falhas devido às questões de confiabilidade e segurança. Esta tese se propõe avaliar diversos modelos RPN em condições adversas, como falhas do tipo bit-flip devido a fenômenos transitórios ou permanentes. Esta tese também propõe uma técnica de detecção de falhas baseada em codificação AN, focada em aceleradores de RNPs, empregados em sistemas críticos de segurança. Devido aos altos padrões exigidos, microarquiteturas empregadas em tais sistemas devem ser capazes de detectar mais de 99% de falhas em seu sistema. Além da alta robustez proporcionada pela detecção baseada em codificação AN, a solução possui implementação não custosa, principalmente quando aplicado em conjunto com a solução inovadora de quantização baseada em códigos AN. Em questões de segurança, os métodos de ofuscação de RNPs baseados em treinamento proporcionam uma excelente proteção aos dados sensíveis, como os pesos. Contudo, tais técnicas possuem falhas nas quais informações importantes são vazadas, como a distribuição das classes resultante das classificações. Além disso, soluções de ofuscação têm de ser escaláveis, a fim de proteger todo o portfólio dos provedores de modelos. A técnica de ofuscação baseada em trocas provê uma solução robusta, segura e escalável para a proteção dos pesos das RNPs, evitando assim o acesso illegal aos dados.

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Doctor of Science (D.Sc.)

## RESILIENT AND SECURE DEEP LEARNING-ORIENTED MICROARCHITECTURES

Brunno Figueirôa Goldstein

June/2022

Advisors: Felipe Maia Galvão França Sandip Kundu Alexandre Solon Nery

Department: Systems Engineering and Computer Science

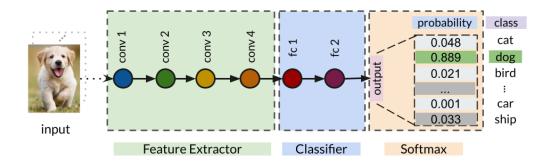

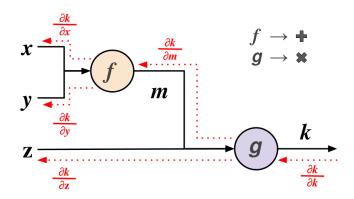

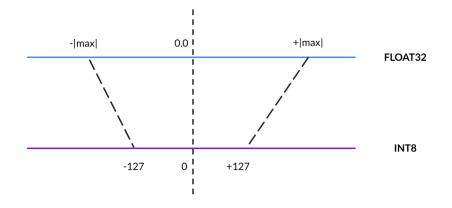

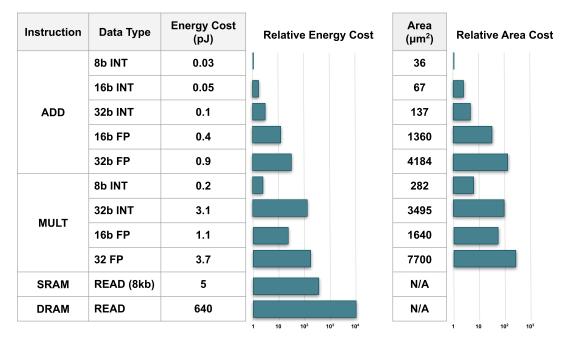

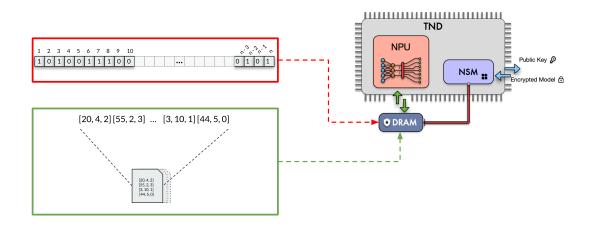

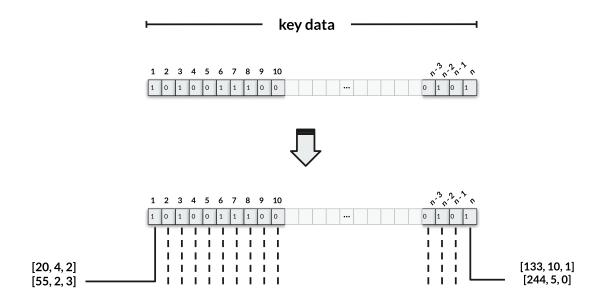

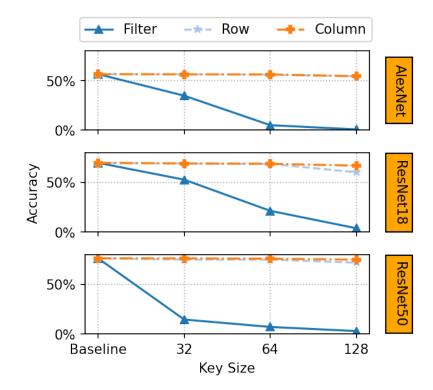

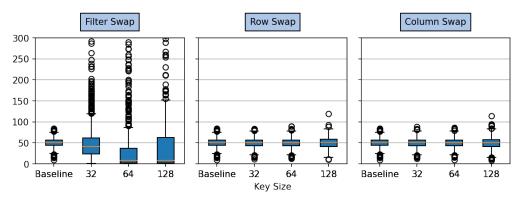

Deep neural networks (DNNs) have emerged as crucial methods for solving complex problems in various domains, including computer vision, natural language processing, and recommendation systems. An ideal DNN-based system should accurately make predictions or classifications based on some input data with no interference from the external environment. However, DNN-based systems are susceptible to failures due to reliability and security issues. This thesis evaluates many compressed DNN models under faulty conditions like bit-flips due to transient or permanent faults. Then, an AN-based detection scheme targeting DNN accelerators deployed into safety-critical systems is proposed. Due to the high compliance standards, microarchitectures employed in this type of system must provide a detection capability of 99% of faults. Also, the AN-based detection offers a lightweight solution, particularly when incorporated with the novel AN code-aware quantization technique proposed in this thesis. Training-based obfuscation techniques have been successfully employed to protect DNN models from illegal access to sensitive data, such as the parameters. However, crucial information such as the output class distribution can be leaked to attackers, indicating that the target model has been compromised. Additionally, an obfuscation scheme must provide a scalable way to protect the model providers' portfolios. The novel swap-based obfuscation scheme provides a robust obfuscation of the DNN model parameters through a scalable and secure solution, avoiding any illegal access and use of the model by non-authorized entities.

# Contents

| Li            | List of Figures xii   |         |                                                                                                                           |    |  |

|---------------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------|----|--|

| $\mathbf{Li}$ | st of                 | Tables  | xv                                                                                                                        | ii |  |

| 1             | $\operatorname{Intr}$ | oducti  | on                                                                                                                        | 1  |  |

|               | 1.1                   | Contri  | $\operatorname{bution}$                                                                                                   | 5  |  |

|               | 1.2                   | Thesis  | Outline                                                                                                                   | 6  |  |

| <b>2</b>      | Bac                   | kgroun  | d                                                                                                                         | 7  |  |

|               | 2.1                   | Neural  | Networks                                                                                                                  | 7  |  |

|               |                       | 2.1.1   | Types of NN Architectures                                                                                                 | 9  |  |

|               |                       | 2.1.2   | Convolution Neural Networks                                                                                               | 2  |  |

|               |                       | 2.1.3   | Use Case Architectures                                                                                                    | 2  |  |

|               |                       | 2.1.4   | Use Case Datasets                                                                                                         | 4  |  |

|               |                       | 2.1.5   | Compute Optimization Techniques                                                                                           | 4  |  |

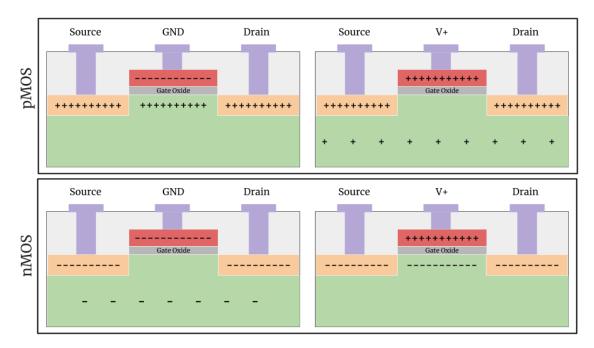

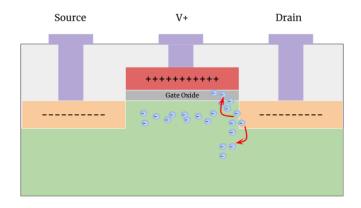

|               | 2.2                   | Reliab  | llity $\ldots \ldots 2$ | 1  |  |

|               |                       | 2.2.1   | Terminology                                                                                                               | 2  |  |

|               |                       | 2.2.2   | Types of Faults                                                                                                           | 3  |  |

|               |                       | 2.2.3   | Source of Faults                                                                                                          | 4  |  |

|               |                       | 2.2.4   | Types of Redundancy                                                                                                       | 0  |  |

|               |                       | 2.2.5   | Assessment Methodologies                                                                                                  | 4  |  |

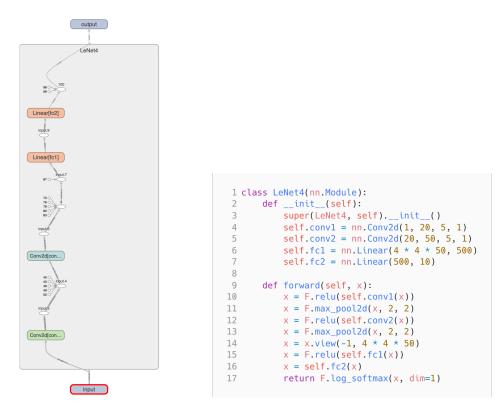

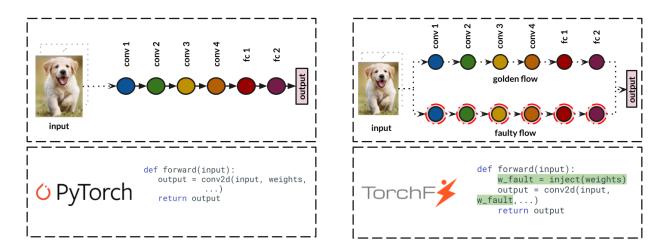

| 3             | Tore                  | chFI: I | ONN Fault Injection Framework 3                                                                                           | 6  |  |

|               | 3.1                   | Back-e  | nd                                                                                                                        | 7  |  |

|               | 3.2                   | Compi   | utational Graph                                                                                                           | 7  |  |

|               | 3.3                   | Front-e | end                                                                                                                       | 7  |  |

|               | 3.4                   | Dynan   | nic Runtime Patching                                                                                                      | 8  |  |

|               | 3.5                   | Fault I | $Models  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                 | 9  |  |

|               | 3.6                   | Curren  |                                                                                                                           | 0  |  |

|               | 3.7                   | Relate  | Work                                                                                                                      | 0  |  |

| 4        | $\mathbf{Rel}$    | iability Evaluation of Compressed Deep Learning Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>42</b>  |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 4.1               | Evaluation Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44         |

|          |                   | 4.1.1 Fault Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44         |

|          |                   | 4.1.2 Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45         |

|          | 4.2               | Experimental Analysis and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46         |

|          |                   | 4.2.1 Models and Datasets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47         |

|          |                   | 4.2.2 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47         |

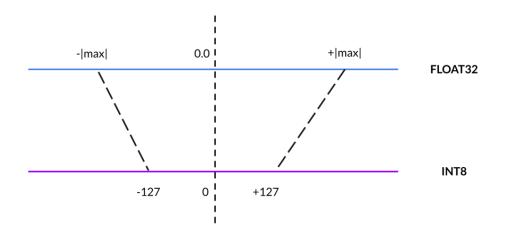

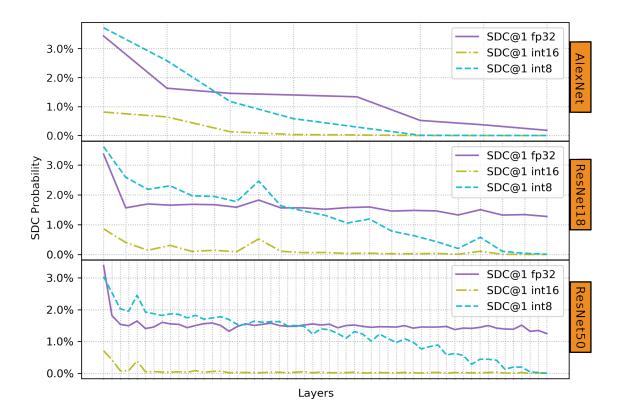

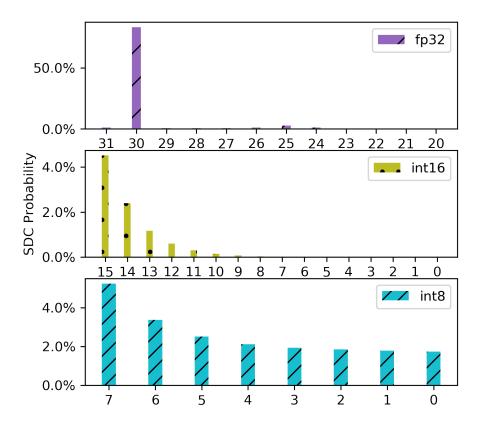

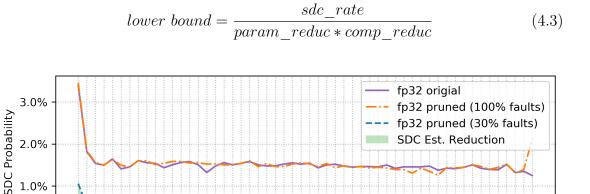

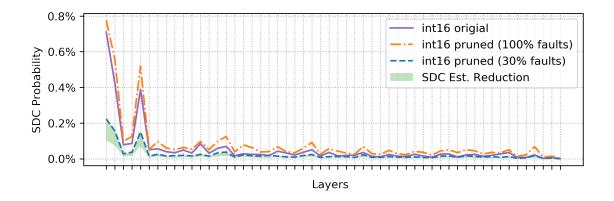

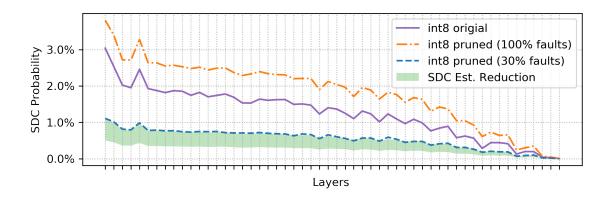

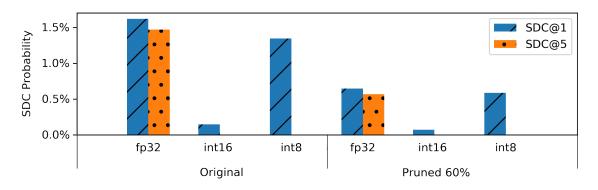

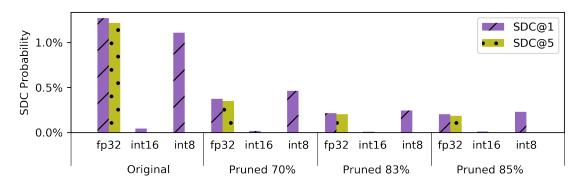

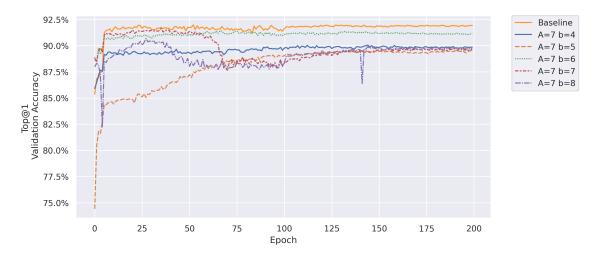

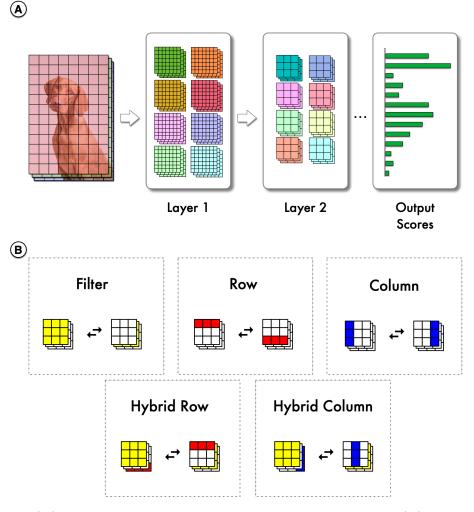

|          |                   | 4.2.3 Quantization Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47         |

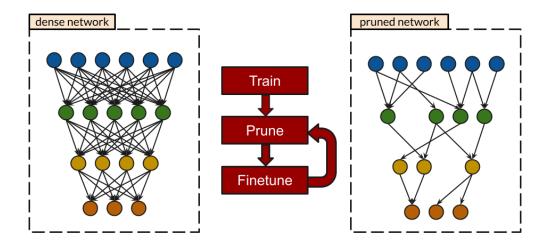

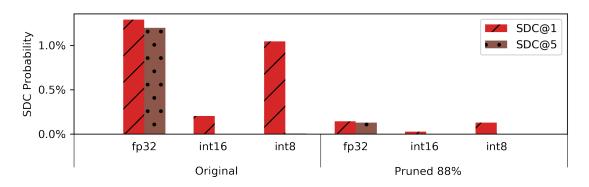

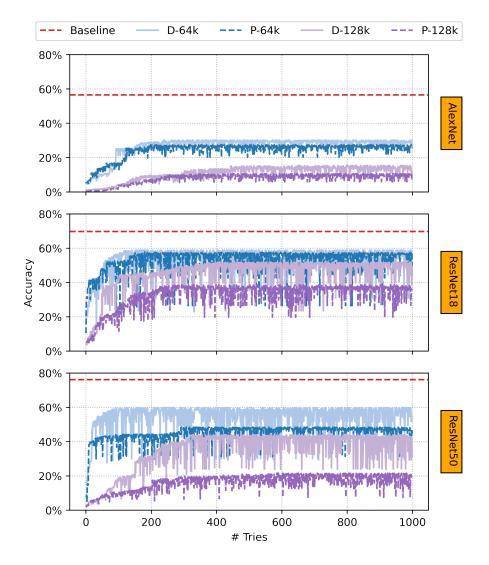

|          |                   | 4.2.4 Pruning Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49         |

|          |                   | 4.2.5 Overall Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52         |

|          | 4.3               | Concluding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54         |

|          | 4.4               | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54         |

| <b>5</b> | T i a             | htweight Ennen Desilionen Mechanism for Deep Neural Net                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

| 9        | wor               | htweight Error-Resiliency Mechanism for Deep Neural Net-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55         |

|          | <b>wor</b><br>5.1 | Arithmetic Error Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>5</b> 5 |

|          | 0.1               | 5.1.1       AN Code       AN Code       An and a state of the st |            |

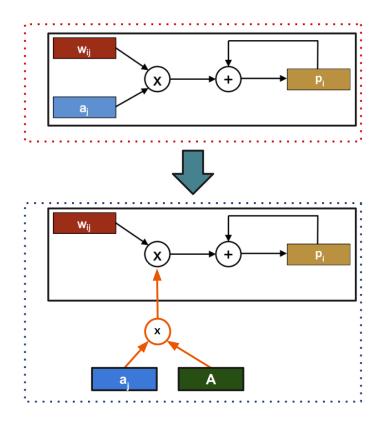

|          | 5.2               | Error Resilient DNN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|          | 5.2               | Fault Model   Fault Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|          | 5.4               | Premises and Scopes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|          | 5.5               | Experimental Analysis and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|          | 0.0               | 5.5.1 Models and Datasets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|          |                   | 5.5.2 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

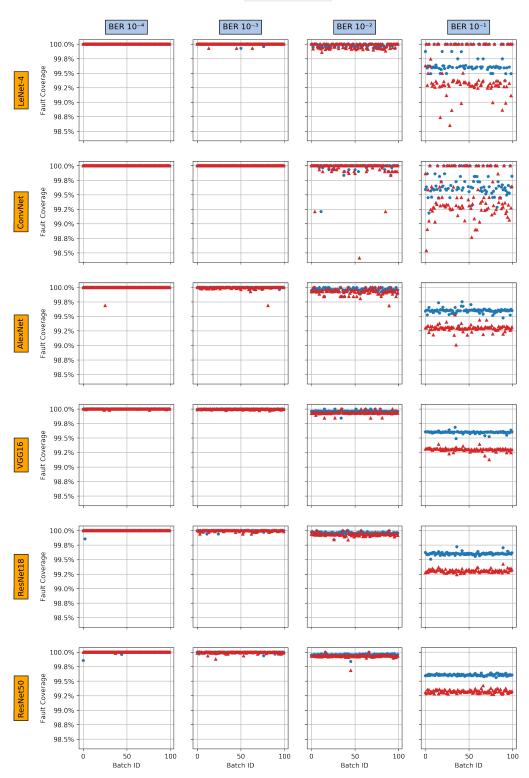

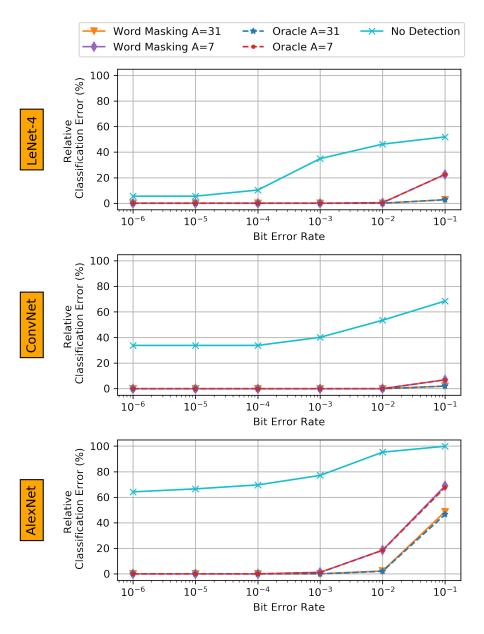

|          |                   | 5.5.3 Error Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

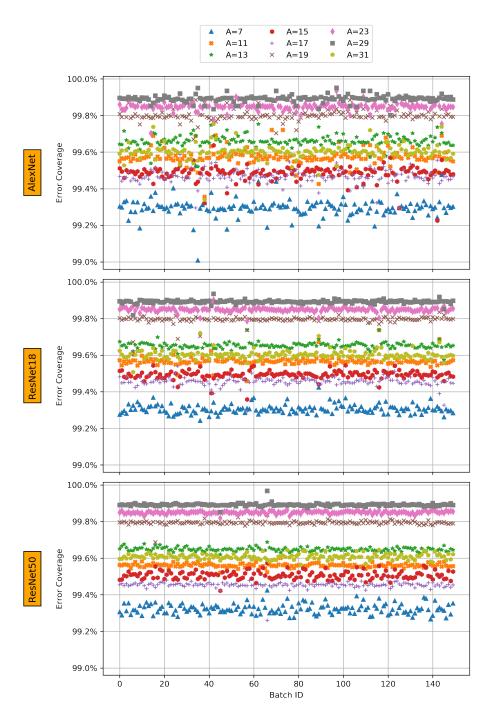

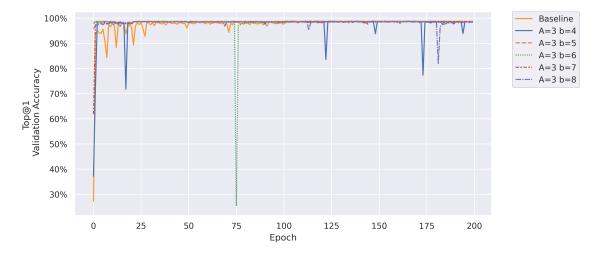

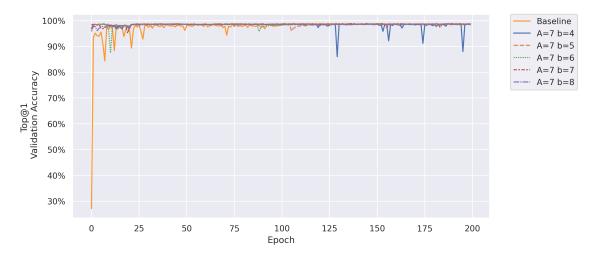

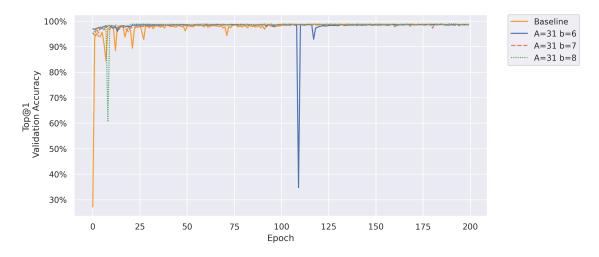

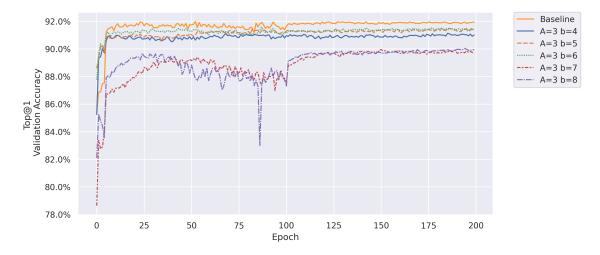

|          |                   | 5.5.4 Impact of A's Choice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

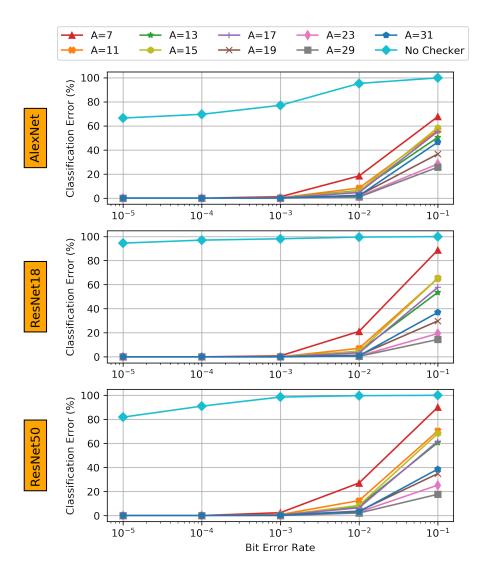

|          |                   | 5.5.5 Error Mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|          | 5.6               | Concluding Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70         |

|          | 5.7               | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|          |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

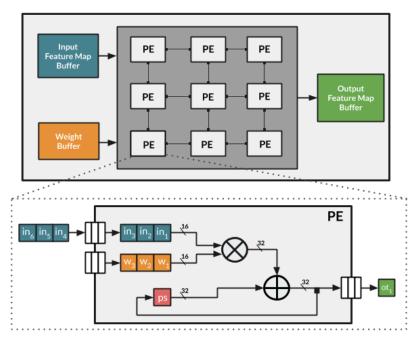

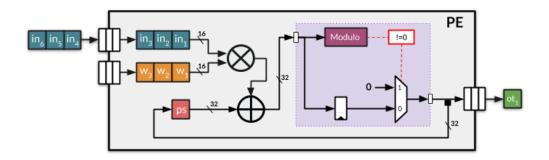

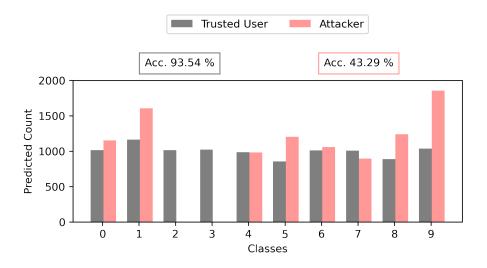

| 6        | Har               | dware and Software Co-Design for Resilient Deep Learning Ac-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|          | cele              | prators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73         |

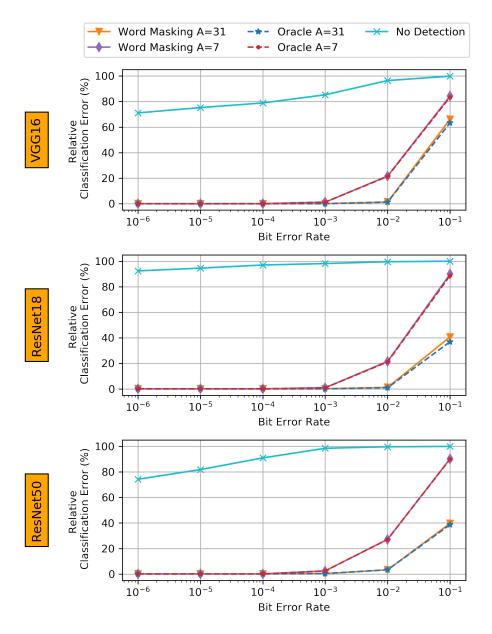

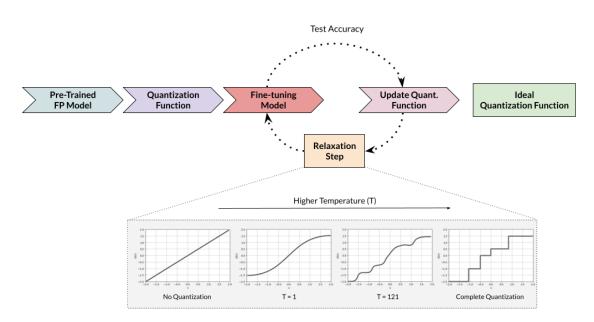

|          | 6.1               | AN Code-Aware Quantization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74         |

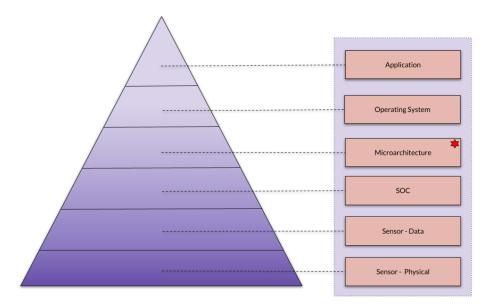

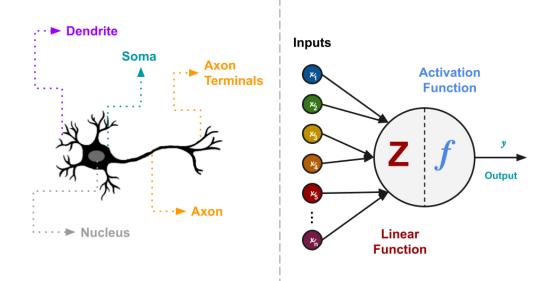

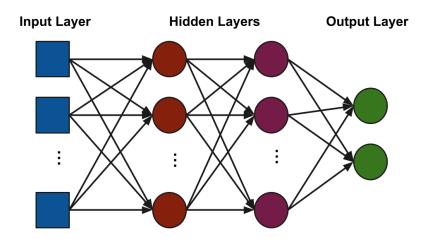

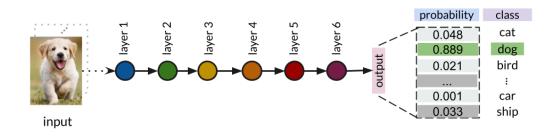

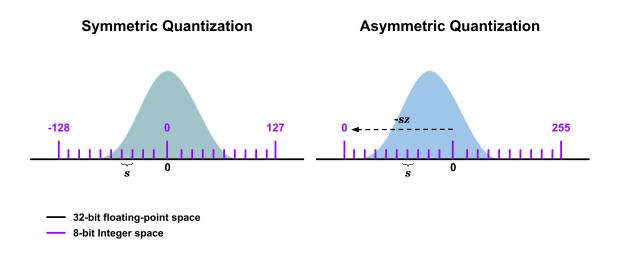

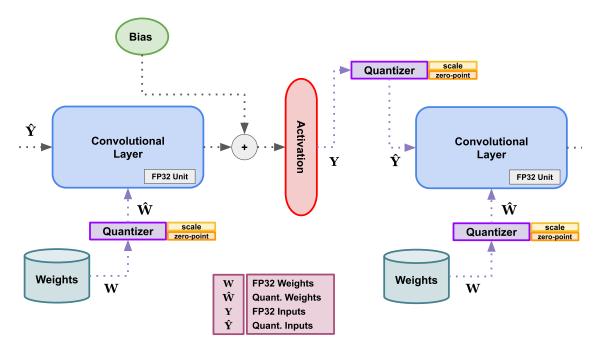

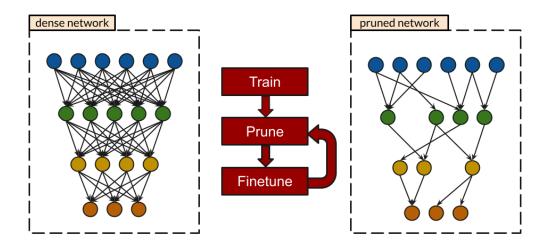

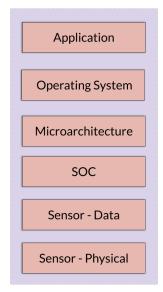

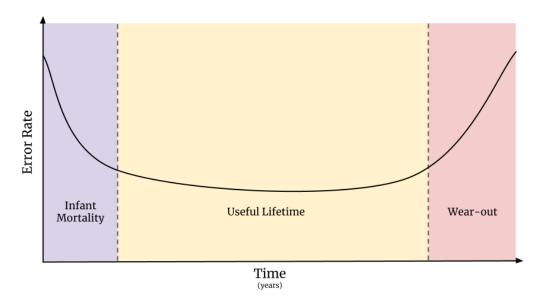

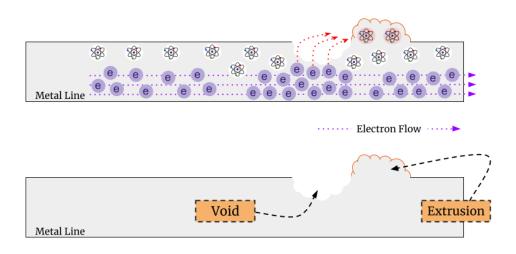

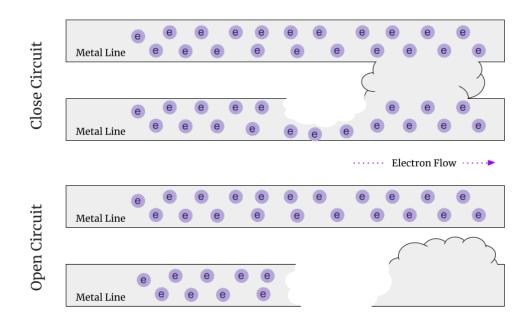

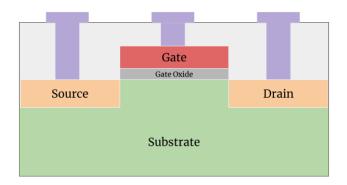

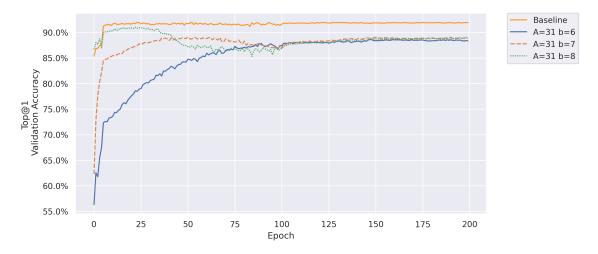

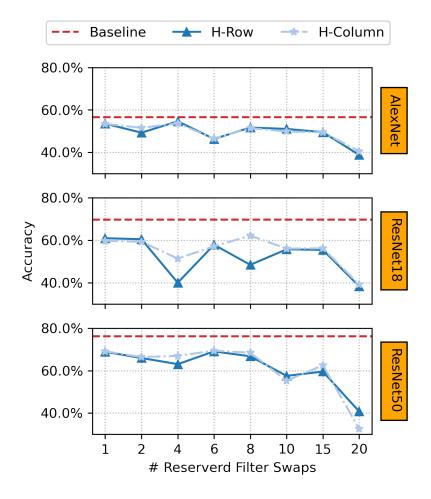

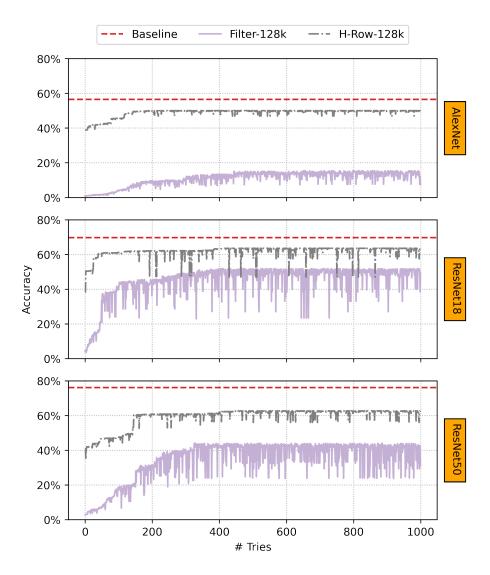

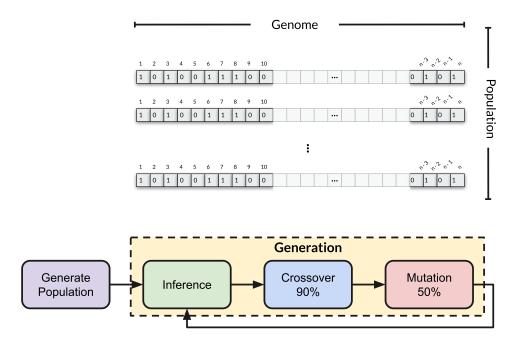

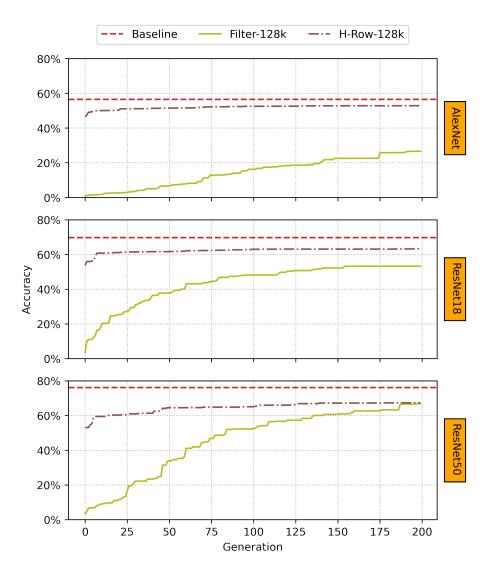

|          | 6.2               | Experimental Analysis and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76         |